Page 1 of 1

delay between PWM

Posted: Fri Feb 25, 2011 10:59 am

by ELMAY

hi sir

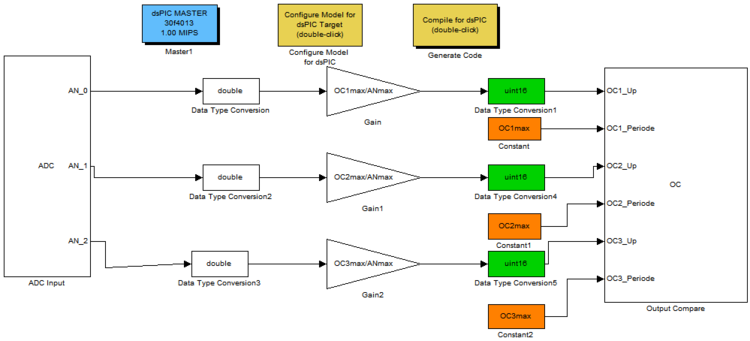

I made this model to generate 3 PWM I compile without errors

This now I ask the following:

how can there be a delay between these 3 signals?

ELMAY

Re: delay between PWM

Posted: Sat Feb 26, 2011 8:49 pm

by LubinKerhuel

Here is your model:

- Elmay's model Commande_IGBT

ELMAY wrote:

how can there be a delay between these 3 signals?

I do not think there is a robust way to do it.

Anyway, you may try the

Output Compare Hardware (OC (HW)) (instead of the Output Compare (

OC)) block which I used for

picooz motor control or this

other example .

With

OC (HW) block, mode 16 makes you able to set for each channel the instant at which you want a rising edge and at which instant you want a falling edge. However, due to the way it works, a PWM duty cycle may be false for one period when you are modifying values.

Lubin